非常簡單筆記一下從頻率變化功能理解 PLL 和 DLL 的差異。

會從 block diagram 和用途兩個方向說明。

不會解釋數學和電路 (因為都超出我的理解範圍了... QQ)

【0. 前言】

IC 設計時經常需要把 clock 推給各處的元件使用,會需要使用 buffer 增加推力。但是經過 buffer 後 clock 的相位會延遲。如果想要 buffer 後的 clock 相位跟 input clock 相同,就需要一個回饋機制,來確保 input clock 和 output clock 其相位(phase)及頻率(frequency)是一致的。

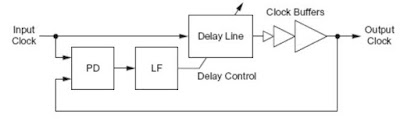

PLL 和 DLL 技術都有這樣的功能,最主要的差異是 PLL 電路中掛一個 VCO(Voltage Control Oscillator 電壓控制振盪器) 推進 buffer;而 DLL 將 input clock 再經過一些額外的 Delay Buffer 調整相位後再拉進 增加推力的 buffer。

【1. Sub Block 解釋】

- PD : Phase Detector (相位偵測器)

- 可將兩個輸入訊號的相位進行比較,並輸出誤差

- 也有高級款 PFD Phase Frequency Detector (相位頻率偵測器)。同時比較兩訊號的相位和頻率。

- 如果相比的兩個訊號是一倍頻,通常 PD 就夠用。

- 但是訊號操作的頻率很廣,fMax/fMin 超過兩倍,即便 input ouput 是一倍頻的關係,用PFD比較保險。

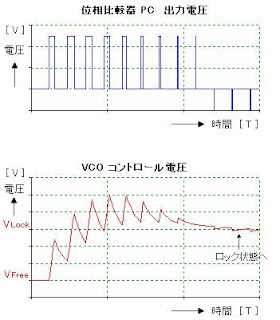

- [圖1-1]上圖藍線波形就是 PD 輸出結果,其high寬度越寬,顯示 buffer 後 clock delay 較大,後面就需要把頻率調快一點。

|

| [圖1-1] PLL の 基本動作 |

- LF : Low pass Filter (低通濾波器)

- 將 PD 後的訊號高頻部分濾除,可降低調整時造成輸出頻率變化的震盪幅度。

- 使後續頻率調整變化不能太劇烈,不然 setup time 或 hold time 難以控制。

- Delay Line (訊號延遲器)

- DLL 中用電壓去控制訊號 Phase Delay 量,是一些額外的 buffer 構成。

- Oscillator (振盪器) 是 VCO ,電壓控制振盪器

- PLL 中用電壓去控制振盪器振出的頻率及相位,[圖1-2]為一種 VCO 作法。

【2. 比較】

- 架構差異

- PLL 和 DLL 主體架構都是 PD + LF + 調控訊號模組。

- PLL 以 VCO 調整訊號。

- DLL 以 Delay Line 調整訊號。

- 應用差異

- PLL 的 clock 是重新產生的,他的頻率跟 input clock 可以脫鉤,可以用來做倍頻,甚至是非整數倍頻電路。

- DLL 的 clock 是一堆 delay buffer 產生,頻率還是跟 input clock 相同,無法用來做倍頻。

- 也因為 DLL 用一堆 delay buffer,可以產生很多不同 phase 訊號。也許可以拿來調整 setup time/ hold time。

- 產生不同 phase 的功能 PLL 也有。如 [圖1-2] 這個架構的 VCO 用一些 inverter 構成,每個 inverter 的接點也可以產生不同相位的訊號

- 其他

- PLL 因為重新產生頻率,有兩個風險:

- VCO 如果故障,就 QQ 了 。DLL 只要 input clock 沒有消失,output clock 大致安好。

- VCO 的起始頻率跟目標頻率可能會差很多

- [圖2-1] 為 PLL 電路製作 N/M 倍頻,在 input clock 做 1/M 倍頻,feedback clock 做 1/N 倍頻拉入 PD 比較,決定 VCO 調整快慢。 穩態後 output clock 成為 N/M倍頻

|

| [圖2-1] PLL Block Digram ( N/M 倍頻) |

|

| [圖2-2] PLL Linear system |

- [圖2-3] 顯示 DLL 產生的 clock 無法變頻,只能改變 phase。

|

| [圖2-3] DLL Block Digram |

|

| [圖2-4] DLL Linear System |

【3. 小結】

【Reference】

- CMOS VLSI design Lecture 22:PLLs andDLLs

- 時鐘的相關概念

- PLL の 基本動作

延伸閱讀:

留言

張貼留言